文摘

冯诺依曼体系结构基于计算机分离计算和存储(即计算模块之间的数据传递(处理器)和内存块)。往复运动的数据导致了现代计算机的基本限制,被称为内存墙。逻辑内存(LIM) /内存计算(IMC)方法旨在解决这一瓶颈通过直接计算内存单元内部从而消除能源密集型和耗时的数据移动。最近的一些文学作品,提出实现逻辑函数(s)新兴电阻直接使用数组存储设备(例如,记忆电阻器RRAM / ReRAM PCM, CBRAM, OxRAM, STT-MRAM等等),而不是使用传统晶体管进行计算。数字系统的逻辑/ embedded-side(如处理器、微控制器)可以大大受益于这种LIM实现。然而,纯数字系统的存储器端(ssd,企业存储等)不会受益太多等LIM方法当内存数组用于逻辑他们失去了核心功能的存储。因此,还需要一种方法补充现有LIM技术,更有利于数字系统的储存;一个内存数组不是让计算能力的成本他们现有的存储状态。从根本上说,这将需要记忆nanodevice数组同时能够存储和计算的。在本文中,我们提出一种新型的同步逻辑内存(SLIM)方法是补充现有LIM方法在文学。通过大量的实验,我们展示小说苗条bitcells (1 t-1r / 2 t-1r)组成non-filamentary双层模拟OxRAM设备NMOS晶体管。 Proposed bitcells are capable of implementing both Memory and Logic operations simultaneously. Detailed programming scheme, array level implementation, and controller architecture are also proposed. Furthermore, to study the impact of proposed SLIM approach for real-world implementations, we performed analysis for two applications: (i) Sobel Edge Detection, and (ii) Binary Neural Network- Multi layer Perceptron (BNN-MLP). By performing all computations in SLIM bitcell array, huge Energy Delay Product (EDP) savings of ≈75× for 1T-1R (≈40× for 2T-1R) SLIM bitcell were observed for edge-detection application while EDP savings of ≈3.5× for 1T-1R (≈1.6× for 2T-1R) SLIM bitcell were observed for BNN-MLP application respectively, in comparison to conventional computing. EDP savings owing to reduction in data transfer between CPU ↔ memory is observed to be ≈780× (for both SLIM bitcells).

介绍

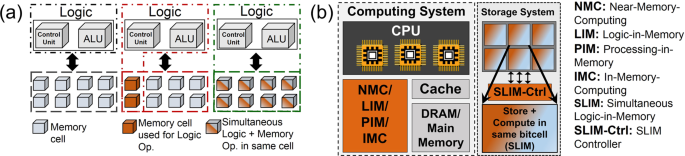

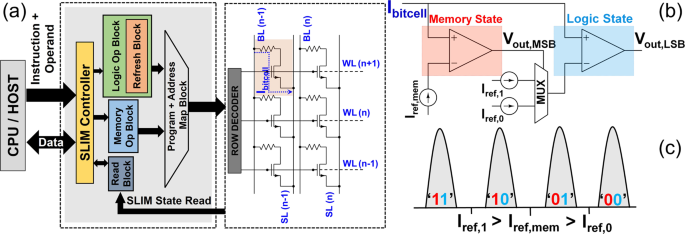

在过去的几十年里,计算单元之间的性能差距(数据处理)和内存单元(数据存储)增加了,俗称内存墙1。是观察到的许多计算任务,大部分的时间和精力消耗在处理器和内存之间的数据传输单元,而不是计算本身2。每个失败的结果,字节(内存带宽每个处理器浮点操作)去年五十年一直在下降3。增加数据量的聚结和需要执行数据密集型应用程序具有有限的计算能力和位置使这种不平衡今天更具挑战性。应对这些挑战,提出了各种解决方案,从设备到系统架构的水平。缓存层次结构提出了帮助改善内存访问延迟引入复杂性为代价的,如缓存一致性和安全漏洞3。其他措施包括空间架构的广泛使用(分布式片上内存接近计算单位)启用并行使用向量处理单元,与大量的核心4。此外,加速器设计来匹配特定的数据流计算算法5。三维记忆,商业化是混合内存数据集6和高带宽内存7芯片提出了满足要求的高数据传输速率和高存储密度。这些提供更高的带宽和降低一个数量级访问由5×能源相对于现有的二维后发展出8。进一步转移,新兴的非易失性记忆(NVM)引入到传统的内存层次结构来减少计算和数据之间的“鸿沟”单位9。有前途的解决方案来消除这些瓶颈是由“逻辑内存”(LIM) / (PIM)方法处理内存10,11,12,13,14,15,16,17,18,19,20.,21,22,进行计算在- - - - - -原地数据的确切位置23。在这些方法10,11,12,13,14,15,16,17,18,19,20.,21,22,重点是将输入变量或/和逻辑输出存储在内存bitcell(见表1)。LIM提供了一个明显的优势通过减少延迟和能源的负担内存墙。然而这些方法仍然使用传统的冯诺依曼体系结构试图计算在物理附近(通常在主存)的数据。这种协同定位的内存/数据和计算(使用逻辑数组)的过程更快。存储内计算也被提出24,但在这种情况下也存储内存(硬盘/ SSD)被视为只是only-storage旁边放置一个处理器。因此本单元本身就像一个迷你电脑。使用高密度存储记忆本身计算将基本或突破性的影响减轻冯诺依曼瓶颈。此外,将计算资源只有在缓存/内存并没有解决新兴大数据的挑战,数据集太大,适合在主存。为了解决这个问题,我们提出一个新颖的同时Logic-in-Memory (SLIM)各级方法可有效的内存层次结构。在现有LIM方法,当某个存储单元执行逻辑操作不能同时用于其固有的内存或者存储功能,而在苗条同一存储单元可用于存储功能和逻辑功能同时在空间(硅区)和时间(时钟周期)。在拟议的苗条的方法(表1),输入变量不是存储在bitcell,而最初的记忆状态保存。图1(一)显示不同的体系结构概念:冯·诺依曼体系结构,用于今天电脑,最近LIM架构和拟议的苗条的架构。图1 (b)显示分离处理器和内存/存储(冯诺依曼体系结构)。它还展示了一个理想的概念计算系统LIM和苗条,使各级计算能力的内存层次结构。

然而,这种新的苗条的架构需要计算内存设备既可以存储数据和计算同时,通常通过物理设备或其他物理定律。由于其独特的性质,新兴NVMs(如相变记忆(PCM),基于氧化物的RAM (OxRAM),自旋转移力矩MRAM (STT-MRAM)等)已经证明自己是很有前途的技术LIM /苗条的方法。他们提供non-volatility连同一个大电阻窗口支持明显歧视州“1”和“0”(一些提供多层次功能(多层陶瓷))。在这些候选人中,OxRAM是一个非常有吸引力的竞争者,因为它可伸缩性、CMOS兼容,低功耗、高运行速度和耐力。双层OxRAM已知设备展览优秀的多层陶瓷行为由于non-filamentary自然切换25。利用这些属性的模拟双层OxRAM设备我们建议1 t-1r / 2 t-1r苗条bitcells和一种新的编程方法。我们表明,使用苗条的方法模拟OxRAM可以同时——(i)执行逻辑操作在- - - - - -原地,(ii)存储的输出逻辑操作,(iii)保留以前存储的内存状态(即值存储在单元逻辑运算前)和(iv)阅读最终逻辑输出和存储内存值,同时使用相同的bitcell。

实验结果

OxRAM设备制造和表征

苗条Bitcell

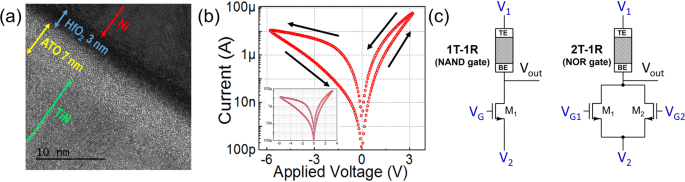

第四特区曲线独立OxRAM设备(图制作的2(一个)苗条bitcell如图2 (b)。由于其non-filamentary,模拟电阻切换、阻力的堆栈展品高度可再生的行为可以以连续的方式逐步调优应用电压刺激,如补充图所示S1。我的D- vDS和我D- vGSNMOS晶体管的特性补充图所示S2。图2 (c)展示了我们的提议1 t-1r和2 t-1r苗条的bitcells。(V出)OxRAM连接到NMOS排水终端(s),和TE (V1)用于应用直接编程信号(P1和P2)。门终端(s)的NMOS晶体管(s) (VG1 t-1r;VG1和VG22 t-1r)用于加载期间操作数作为控制信号的逻辑操作。身体终端(s)的NMOS晶体管(s)(是)接地(不做空源终端)。NMOS晶体管(s)帮助:(i)苗条的实现,(ii) current-compliance(细丝的OxRAM设备),和(3)细胞的选择。在苗条bitcell OxRAM设备,我们使用VG= 4 V,对应于RNMOS≈1 kΩ和重置我们使用VG= 10 V。高VG需要在我们bitcell OxRAM设备尺寸大,片外使用离散NMOS晶体管。

苗条的概念

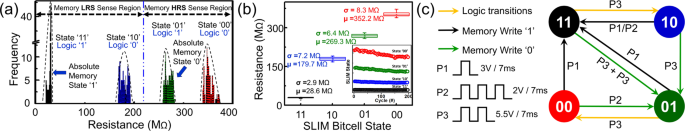

苗条从根本上不同于其他LIM架构之前报道的文献10,11,12,13,14,15;因为它允许使用一个给定的存储单元,同时执行逻辑操作,同时保留其实际内存状态。实现同时无损逻辑运算我们提出以下方法——首先,我们选择4不同的电阻状态(写上:“11”,“10”,“01”和“00”图3(一个)连续的)实现OxRAM阻力水平(补充图S1)。不同国家的基础上选择:(i)编程再现性,(2)易州际之间的转换4水平;即要求更少的类型的编程脉冲(信号P1, P2, P3图3 (c)),和(3)兼容性同时内存/逻辑——读操作。每个4选中状态(“11”,“10”,“01”,“00”)分配——逻辑(' 1 ' / ' 0 ')和内存(LRS /小时)分别定义(见图3(一个))。读出放大器阈值和内存状态感应窗口定义,这样2状态躺在记忆LRS意义地区其他地区分别在内存中2小时感觉。在图3(一个),“11”和“10”躺在记忆LRS区域并分配逻辑“1”和逻辑“0”值分别。而州“01”和“00”躺在记忆小时地区和分配逻辑“1”和逻辑“0”值分别。因此,这样的状态分配,系统有两个表示;逻辑“1”,逻辑“0”,LRS内存小时和记忆。在执行任何逻辑运算,苗条的编程方案允许状态转换只在逻辑(' 1 ' / ' 0 ')水平的一种特定内存区域(即逻辑“1”↔' 0 '小时内或在LRS区域是允许的,但逻辑“1”↔通过小时↔LRS ' 0 '是不允许的)。因此任何最初记忆状态存储在bitcell可以保留即使执行逻辑操作。一个读操作可以同时读取和解码的记忆——在设备和逻辑值。

苗条的状态定义

根据设备的变化,我们认为是一个可靠的抵抗范围和抵抗窗口4苗条的州。以下是每个苗条的电阻范围状态:

状态”11”:电阻的设备范围从20 MΩ33 MΩ意思(μ)= 28.69 MΩ。这是绝对内存状态”1”即在内存写“1”操作装置可这种阻力状态。

状态”10”:电阻的设备范围从170至190 MΩMΩμ= 179.74 MΩ。

状态”01”:电阻的设备范围从260至280 MΩMΩμ= 269.36 MΩ。这是绝对内存状态”0”即在内存写“0”操作装置可这种阻力状态。

状态”00”:电阻的设备范围从340至360 MΩMΩμ= 352.17 MΩ。

图3 (b)显示了实验程序分布4苗条的阻力水平和他们的自行车耐力。耐力测试是使用恒压应力(CVS)程序进行的。苗条的四个州都通过使用编程信号(P1、P2、P3)在一个序列,序列是重复200次测试耐力。苗条的方法论的状态图如图3 (c)。它说明了所需的编程信号(P1, P2, P3)和可能的苗条的州际转换而实现任何逻辑或内存操作。应用P1和P2脉冲,OxRAM设备的阻力逐渐降低时应用P3脉冲电阻增加。

实验验证

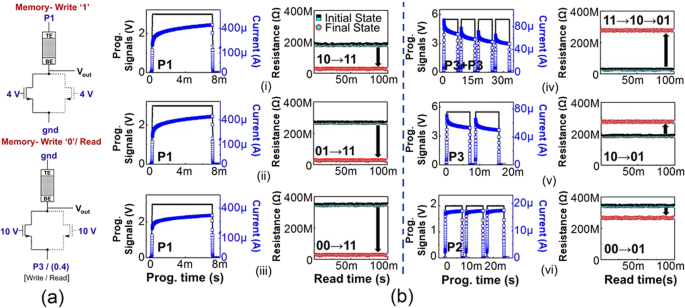

记忆写操作

这些指的是纯粹的存储操作的目的只是储存一点(' 1 ' / ' 0 ')在苗条bitcell (1 t-1r / 2 t-1r)。数据可以存储在bitcell通过内存写——“1”(即绝对内存状态“11”,LRS)或内存写——“0”(即“01”绝对记忆状态,小时)。记忆写操作期间,bitcell编程绝对内存状态(如图3 (a、c))。图4(一)显示了内存写操作精确bitcell编程方法。在内存写' 1 ',编程信号P1是应用于终端V1第五、终端2是接地和VG保持在4 V。而在内存中写“0”,终端V1接地,P3编程信号应用于V终端2和VG是由10 V。图4 (b)显示内存的详细实验结果写“1”(图4 (b) (》)写“0”(图)和内存4 (b) (iv-vi)从所有可能的初始状态。我们可以观察到设置转换图4 (b) (》、vi)随着当前通过OxRAM设备逐渐增加在应用编程脉冲P1和P2。同样,重置开关明显在图4 (b) (iv, v)随着当前通过OxRAM设备逐步减少在应用编程脉冲P3。在设置编程≈100μ一到450μ电流流动而在重置编程≈40μ一到80μ电流流经bitcell。

(一个)信号例子申请内存写' 1 '和内存写“0”。在括号中指定阅读条件。(所有女士脉冲持续时间= 7)(b)实验测量内存写“1”操作(项目设备状态“11”)与设备的初始状态为:(i)“10”, (2)“01”, (3)“00”。记忆写' 0 '操作(项目设备状态“01”)与设备的初始状态(iv)“11”, (v)“10”和“00”(vi)。蓝线:瞬变电流通过OxRAM设备。黑线:P1、P2、P3(应用信号)。黑色广场:初始阻力状态,红色圆圈:最后的抵抗状态后苗条的操作。请注意在(iv, v)瞬变电流通过OxRAM设备到期逐渐增加在非易失性电阻连续复位脉冲的应用。注意:(我目前的规模- - - - - -vi)为明确不同示范OxRAM逐步切换的装置。

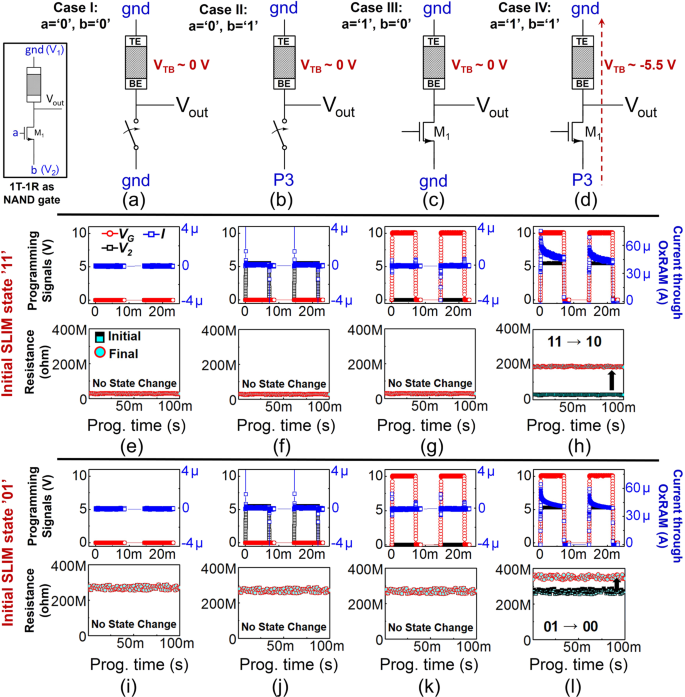

1 t-1r苗条协议(普遍的与非门)

这些指的是纯粹的逻辑操作上执行1 t-1r苗条bitcell (ex - NAND,或者不是等等)。表2介绍了微弱状态映照和真值表实现2-input与非门操作使用单一1 t-1r苗条bitcell。执行逻辑运算之前bitcell最初可能包含任何存储内存状态(即绝对内存状态“11”或“01”),由于之前的记忆操作(s)。虽然实现逻辑运算,苗条bitcell可能接受状态变化但总体内存状态保存。表2显示以前的记忆状态是有效的保存与非逻辑运算后,苗条的美德状态图中描述的任务和编程方法3 (a、c)。所有可能的电路原理图和NAND闪存编程信号比特,2-input (一个,b)操作数组合如图5(模拟)。操作数一个/b被映射到VG/ V2终端分别为bitcell,保持V1停飞。操作数映射的电压条件如下:

一个=b= '0”:在这种情况下,两个VG= V2= 0 V(接地)。

一个= '0”;b= '1”:在这种情况下,VG= 0 V(接地)而V2= 5.5 V。

一个= '1”;b= '0”:在这种情况下,VG= 10 V而V2= 0 V(接地)。

一个= '1”;b= '1”:在这种情况下,VG= 10 V而V2= 5.5 V。在这种情况下,设备将进行重新编程。

四个可能的输入操作数组合:(一个)一个=b= ' 0 ';(b)一个= ' 0 ',b= ' 1 ';(c)一个= ' 1 ',b= ' 0 ';(d)一个=b= ' 1 ';与非真值表,并提出了相应信号映射为每种情况下1 t-1r苗条bitcell。[V结核病= VTE−V是;操作数一个映射到VG= 10 V(7女士长);操作数b映射到V2长)女士= P3 = 5.5 V (7)。实验结果与非逻辑使用1 t-1r苗条bitcell实现设备的初始状态:“11”(e- - - - - -h),“01”(我- - - - - -l)。在四个操作数组合,OxRAM设备开关逻辑小时状态(“10”或“00”)一个=b= ' 1 '。蓝色:瞬变电流通过OxRAM设备。

当一个' 0 ',NMOS晶体管。然而,只有当两个吗一个和b' 1 '(逻辑高),应用编程信号滴在OxRAM经历复位开关。图5(情况)显示试验与非逻辑运算的实现苗条bitcell初始设备状态:“11”(即存储内存LRS / ' 1 '),和图5(我)初始设备状态:“01”(即存储内存小时/“0”)。很明显,连续两个相同的复位脉冲(P3终端V2,操作数b= ' 1 '),由于non-filamentary切换,OxRAM阻力逐渐增加,电流流经设备的减少。类似OxRAM行为以应对连续复位脉冲(P3)也观察到在执行苗条的内存操作(图4 (b))。所有实验反复验证保护初始内存状态逻辑运算。

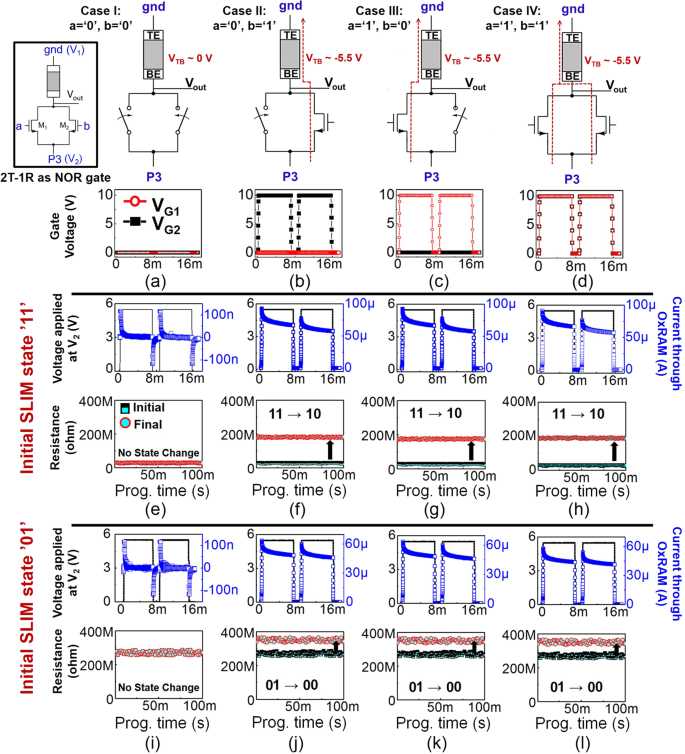

2 t-1r苗条协议(通用或非门)

单个2 t-1r苗条bitcell能够执行多个逻辑操作前也没有,没有,NAND闪存,或者等。额外的晶体管相比1 t-1r bitcell bitcell配置添加更多的功能。表3介绍了微弱状态映照和真值表实现2-input或非门操作使用一个2 t-1r苗条bitcell。类似于1 t-1r苗条bitcell,我们假设2 t-1r bitcell处于绝对内存状态(“11”或“01”)之前执行逻辑操作。表3显示以前的记忆状态是有效的保存每次和逻辑运算。操作数一个/b被映射到VG1/ VG2分别在信号应用P3终端V2第五,保持1停飞。当一个或b是“0”,相应的NMOS(参见图吗6)。然而,当一个或b' 1 '(逻辑高),相应的NMOS,因此应用编程信号滴在OxRAM经历复位开关。图6(情况)显示实验和逻辑运算的实现2日t-1r苗条bitcell初始设备状态:“11”(即存储内存LRS / ' 1 '),和图6(我)初始设备状态:“01”(即存储内存小时/“0”)。

四个可能的输入操作数组合:(一个)一个=b= ' 0 ';(b)一个= ' 0 ',b= ' 1 ';(c)一个= ' 1 ',b= ' 0 ';(d)一个=b= ' 1 ';对应和真值表,提出信号映射为每种情况下2 t-1r苗条bitcell。[V结核病= VTE−V是;VG= 10 V(7女士长);V2= P3 = 5.5 V(7女士长)。实验结果和逻辑使用2 t-1r苗条bitcell实现设备的初始状态:“11”(e- - - - - -h),“01”(我- - - - - -l)。在四个操作数组合,OxRAM设备开关逻辑小时状态(“10”或“00”)一个= ' 0 ',b= ' 1 ';一个= ' 1 ',b= ' 0 '一个=b= ' 1 '。蓝色:瞬变电流通过OxRAM设备。黑线:P3在所有情况下(应用信号)。

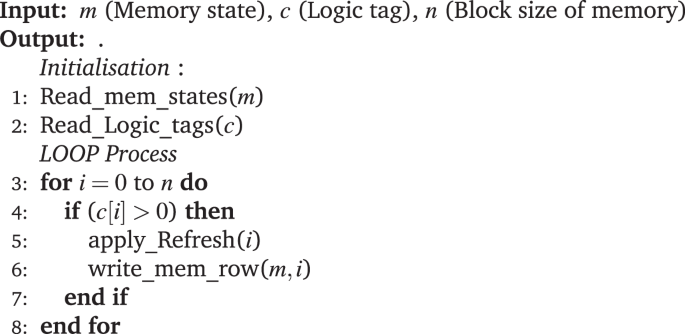

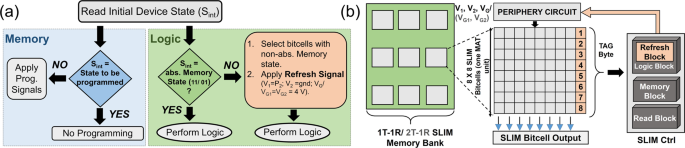

Array-level实现苗条

为了避免可能的阻力状态饱和在多个连续苗条逻辑↔内存操作在一个大2 t-1r苗条bitcell数组,我们定义一个智能SLIM控制协议添加刷新块(图7)。在刷新方案中,首先读取bitcell的初始状态。如果bitcell绝对内存状态(即“11”或“01”),可以直接执行逻辑实现遵循编程方案图中定义3 (c)。然而,以防bitcell处于内存网格工作流状态的状态(即“10”或“00”),刷新应用(即信号P2 V1,V2V =接地,G1= VG2= 4 V)。如图3 (c)、应用的P2总是恢复bitcell逻辑状态(“10”或“00”)对应的绝对内存状态(“11”或“01”)。这使得同一个bitcell接下来的逻辑运算,有效地保留以前的记忆状态。刷新方案可以进一步优化定期通过执行它只在阵列级别,使用标签字节追踪的最后操作苗条垫单元(见图7 (b)为进一步的细节)。苗条垫表明二维苗条bitcell数组。一次,一点整个垫用于逻辑操作,行操作刷新操作可能会启用。算法来解释刷新操作在建筑层面总结了算法1。如图7 (b),一个标签注册是分配给每个苗条垫1比特对应于每一行。在网格工作流bitcells内存状态/行>预先确定的阈值(0.5×n其中n =数量的连续bitcells)相应的标签设置高一些。基于阈值触发标记位确保刷新操作最小化,反过来又有助于减少能源开支苗条bitcell数组操作。

图8(一个)介绍了苗条的控制器实现包括所有数据的细节3 (a、c)和7(一)。它有三个街区控制内存写,逻辑,读操作。有一个额外的控制信号选择内存/逻辑模式。在逻辑块,一个额外的情报是建立实现刷新机制。图8 (b, c)说明了传感机制用于阅读苗条bitcell状态。MSB(最高有效位)和LSB(最低有效位)的微弱状态分别描述了记忆和逻辑状态。在情况下,应用程序只需要读取内存状态,V出,最高有效位我是充分的,(即比较bitcell我对预定义的内存阈值窗口裁判,mem)。解码逻辑状态,另一个与逻辑阈值(例如我裁判,1,我裁判,0应该执行)。在文学,电流放大器(CSA)传感多级州提出了26。

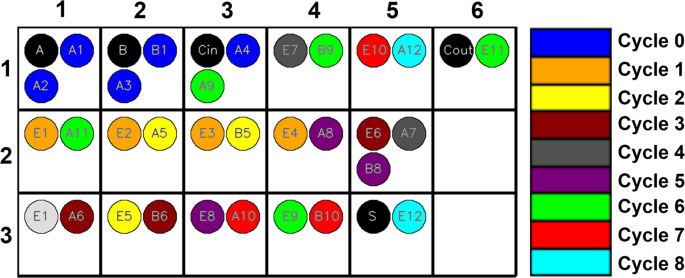

图9显示出完整的加法器的实现(FA)使用提出1 t-1r苗条与非逻辑与准确的周期和bitcell位置映射。映射已经使用一个定制的苗条bitcell编译器派生出来。约束用于推导映射主要有:(1)输入出现在一行,(2)输出不映射到同一行作为输入,和(3)所有操作使用相同的输入和输出行可以并行执行。循环计数显示在图9包括:(1)读周期读取输入行,和(2)苗条的操作周期适当应用编程信号苗条bitcell的终端输出行。表4说明了苗条的扩展方法逻辑操作超出NAND /也不(尽管使用相同的编程信号)。应该注意的是,在所有这些情况下只有一个苗条bitcell需要意识到布尔函数。

苗条的应用分析

拟议的苗条bitcell是逻辑上完全可以实现NAND /没有盖茨(即通用盖茨)。所有其他基本盖茨和算术函数可以被映射实现所需的函数在NAND /也不是盖茨。研究提出了苗条的影响方法逻辑计算我们得到能源和延迟估计基本逻辑门规范化w.r.t.苗条的基础与非门的值(即一个1 t-1r苗条bitcell)和苗条或非门(即一个2 t-1r苗条bitcell)。我们使用了一个近似模型推导交换能量,如情商所示。1其中N表示总可能输入的组合吗x我。Switch_events函数是一个数学模型,确定状态转换的事件在假设每个节点基于NAND /也不是逻辑计算指定的逻辑运算。延迟估计总数派生的逻辑水平所需计算的逻辑函数的基础上计算图像导出使用NAND /也没有逻辑。结果总结在表5。

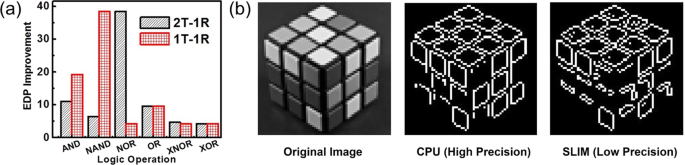

OxRAM设备中使用的实验研究有更大的面积,因此表现出更高的延迟和能源成本。为了执行一个公平的比较先进的架构,我们使用先进的设备参数双层细丝的高频振荡器x设备27,28(补充表所示S1)。图10 ()突出的性能(EDP)比较64位逻辑运算使用传统的CPU执行(英特尔酷睿i5 - 2500桑迪大桥3.3 GHz CPU)和苗条bitcell假设数据是获取从DRAM /苗条bitcell数组。对于CPU,延迟时间和精力值从技术报告29日,30.一直在考虑。为数据传输总线带宽用于所有内存接口是128位。基于苗条bitcell估计,我们结合线延迟和耗散ird中指定的指导方针31日(节点扩展为28 nm节点被用来估计从14 nm / 16 nm)。能量为1比特逻辑门(1比特操作数)派生和外推n位逻辑门(假设n位操作可以实现并行计算使用n银行苗条bitcell数组)。对于所有给定的逻辑操作,我们可以观察到最低EDP≈4×中获益。进一步分析的影响引入苗条bitcell数组在内存中的实际工作负载,我们进行了两个案例研究(边缘检测和BNN)。

(a) EDP比较来执行64位逻辑操作使用苗条数组w.r.t.传统CPU体系结构(抓取操作数从DRAM (DDR3)), (b)的边缘检测输出的CPU + DRAM(中心)和“CPU +苗条bitcell数组”(右)与原始图像(左)。图片来源:(b)原始图像显示在左边是一个缩放和裁剪版的“BW魔方Gerwin Sturm”(https://www.flickr.com/photos/scarygami/5568844961下许可的),2.0 CC冲锋队(https://creativecommons.org/licenses/by-sa/2.0/)。生成图像中心和正确进行边缘检测)。

我:Sobel边缘检测

一个图像处理的边缘检测的应用进行了分析。与Sobel边缘检测算子,其中包括64×64的卷积图像(如图10 (b))和一个3×3大小的过滤器。3×3 Sobel过滤器操作涉及9×MUL和9×添加操作。实现的复杂性降到最低,4比特精度被认为是使用苗条bitcell阵列相比,完整的8位精度由CPU使用。进位存储架构(CSA)用于实现4比特乘数。此外,4比特脉动进位加法器(RCA)用于计算最终结果。苗条bitcell数组用于分析与垫大小为4 kB大小8×8蔓延与32垫/银行16家银行。平行的比特总数苗条的操作可能是32×16×8 = 4096。由于所有操作4比特精度,8个并行操作可以同时执行一个垫子。因此最大的操作可以并行执行整个苗条bitcell数组是128。基于映射,我们推导出坏的情况下应用程序的延迟和EDP值。对于每个Sobel操作,CPU使用9×IMUL, 9×添加、18×加载和9×存储操作。 Cycle latency and average energy dissipation for each operation is used for calculating EDP. Total Sobel operations performed are 64 × 64 = 4096. Figure10 (b)介绍了边缘检测的结果使用高精度CPU和苗条的精度分别bitcell数组。表6总结了相对EDP比较而言,这两种方法的数据传输和计算操作。它假定数据获取(计算)从主内存(DRAM数组)的CPU。此外,能源和产生的延迟惩罚也考虑由于缓存未命中的情况。苗条的逻辑操作的指令包含在记忆指令的开销降到最低。通过执行所有计算在苗条bitcell数组,总EDP为应用程序减少了1 75×40×t-1r和2 t-1r苗条bitcell数组分别(总结表6)。这个性能优势将更加明显,进一步提高设备技术和基于编译器的优化。从表中也观察到了6在电子数据处理,数据传输储蓄≈780×(1 t-1r / 2 t-1r苗条bitcells)由于减少数据传输(CPU↔内存)作为IMC的结果。计算使用传统CPU体系结构中,所有的操作数都需要从DRAM获取。但是做计算使用苗条,操作数已经出现在苗条bitcell数组(DRAM)一样它驻留在同一位置。因此,CPU需要发送指令和获取结果。

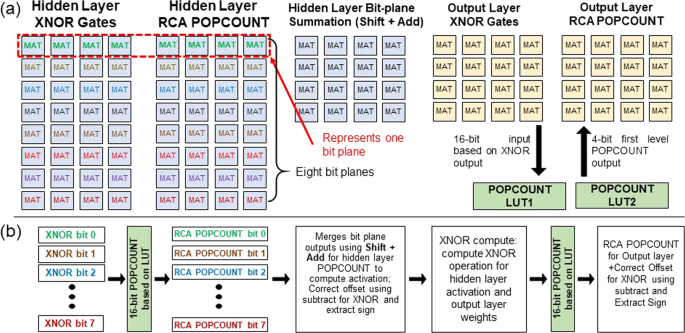

案例二:二进制神经网络——多层感知器(BNN-MLP)

实现BNN-MLP电子数据处理分析32网络的大小784×100×10(补充图所示S4 (a))苗条bitcell阵列(数组大小= 1 MB意识到使用32×32苗条垫)。网络MNIST训练数据集(补充图S4 (b))。计算和XNOR和POPCOUNT操作映射。操作映射总结在图(11日)和的操作序列用于BNN-MLP计算如图11 (b)。第一层的映射是基于层协会(隐藏、输出)其次是操作类型(XNOR POPCOUNT)。隐藏层计算,重量是二进制(1,0),输入是量子化的8位有符号整数,因此8位平面同时也进行了计算。对POPCOUNT操作,第一阶段是使用附近地区实现33(功率估计基于文学34)。第二阶段中间4比特POPCOUNT由求和实现的结果使用基于苗条垫分层加法器树(如图S4 (c))。后POPCOUNT位平面由Shift +添加合并抵消校正紧随其后。激活的神经元计算输出的迹象。在输出层的情况下,所有的计算都是在一个位平面XNOR类似POPCOUNT操作和偏移校正。在我们的研究中,整个计算映射需要6909苗条垫的大小32×32。BNN-MLP映射网络对CPU使用以下指令:负载,商店,XOR,不是,POPCNT,(逻辑左移),添加、子,CMP。详细讨论关于映射和操作调度也提供的补充部分S5。总结在表估计EDP的最终结果6。1 t-1r苗条的基础实现BNN-MLP提供的一个好处≈3.5×相比,基于CPU + DRAM而2 t-1r≈1.6×的实现提供了一个好处。

讨论

OxRAM设备制造为本研究是出于演示的目的,因此大(50μm×50μ米)。进一步扩展OxRAM设备集成芯片上的NMOS选择器将导致显著减少操作电压(设置/重置)。的编程电流non-filamentary OxRAM设备,用于这项研究中,已被证明与设备的有效面积规模35。对细丝的OxRAM设备一个期望变化与扩展变得更糟36然而,以防non-filamentary OxRAM齐次界面切换有助于克服内在操作电流和变异性之间的权衡35。苗条bitcell是基于基本逻辑实现,因此直接级联逻辑门是不可能的。在这个案例研究中,OxRAM装置展品更高的阻力水平由于读取电压水平的选择,这需要精确合理放大器精确确定苗条bitcell外围国家导致了额外的开销。读出放大器的限制可能会轻松通过调优的阻力窗口OxRAM设备。电阻窗口调优可以以多种方式实现材料/接口栈工程等,选择不同的编程和读取电压水平。此外,逻辑实现使用苗条的方法,需要定期刷新操作带来苗条的控制器添加开销。然而,对于高密度存储系统,频率刷新刷新操作将减少和优化的方案可以进一步解决这个问题。苗条bitcell操作依赖于使用写操作来执行逻辑,因此面临着基本限制由于有限的耐力OxRAM设备。我们提供了一个额外的分析讨论策略来解决这一问题的补充材料(见补充部分S6)。分析验证的耐力要求一个BNN-MLP推理操作是典型的疲劳极限内OxRAM设备报告文学37。最好的情况下在我们的分析(补充图所示S5),每一个人独特的苗条bitcell操作映射。使用此策略,≈1012推理操作可以执行与设备耐力(提出了文学38)使用计算内存≈7 Mb。自提出苗条的方法是针对高密度存储系统(大ssd能力> 100年代GBs / TBs),获得大量的苗条bitcells可以假定稀疏映射的逻辑操作。这将减少整个耐力要求。

结论

我们提出了一种新颖的“同时Logic-in-Memory”方法(SLIM)克服冯诺依曼瓶颈。这种方法可以用于计算内存bitcell不失先前存储的内存状态利用双分子层的模拟行为OxRAM设备。OxRAM使用4个不同的内存状态的设备,我们已经通过实验验证的NAND /也不是逻辑1 t-1r / 2 t-1r苗条bitcell同时显示多个复杂的逻辑功能的实现。我们进一步增强的范围苗条bitcell提出编程方案实现其他布尔操作除了使用一个苗条bitcell NAND /或非门。我们还提出了一个苗条的控制器设计和连续刷新计划实现逻辑操作。我们比较苗条的方法的性能与传统CPU +内存的实现两个应用程序:(i) Sobel边缘检测(2)BNN-MLP。分析显示巨大的EDP储蓄≈75×1 t-1r (≈40×2 t-1r)苗条bitcell边缘检测的应用程序而EDP储蓄≈3.5×1 t-1r (≈1.6×2 t-1r)苗条bitcell BNN-MLP申请。使用这种方案,高密度存储可以作为免费的计算资源而不打扰用户的存储数据。

方法

设备制造

模拟电阻切换OxRAM成堆的Ni / 3海里高频振荡器2/ 7海里Al-doped -TiO2(ATO) /锡(从上到下)结构制作遵循一个CMOS兼容的过程。激活装置区域是50μm×50μ米,ATO以及高频振荡器2使用plasma-enhanced沉积原子层沉积(PE-ALD)。透射电子显微镜(TEM)的横截面图像设备堆栈如图2(一个)看到,非晶态电介质双分子层沉积在罐底部电极(是)薄膜均匀性高,ALD的指纹。设备制造流程如下:首先,100纳米厚的锡膜是沉积在热-SiO2(500海里)/硅晶片的物理气相沉积(PVD)、射频磁控溅射。BEs然后由光学光刻图案(第一个面具)和干蚀刻使用电感耦合等离子体(ICP)。底部,厚7纳米ATO介质,然后由交换不同的沉积TiO2和艾尔2O3PE-ALD周期,使用TDMATi (Tetrakis (dimethylamido)钛)和TMA (trimethylaluminum)作为有机前体和O2等离子体作为反应物。上3 nm厚介质高频振荡器2电影,是沉积使用TDMAHf (Tetrakis (dimethylamido)铪)O2等离子体。所有证词都在250°C使用Veeco-CNT斐济F202远程等离子热壁反应器PE-ALD系统。上电极(TE)模式(类似于模式但旋转90°)定义使用第二光学photo-lithography面具和100 nm厚倪TE电影是由直流溅射沉积和图案使用发射技术。最后光刻(第三个面具)和ICP干蚀刻步骤执行打开windows(蚀刻电介质)是接触接触垫。线焊接和包装的最后步骤OxRAM封装。

电气测量微弱bitcell鉴定

我们使用4200年吉时利SCS参数分析仪使用自定义设置(补充图S3)来执行电气测量。吉时利4210大功率SMU(源测量单元)和吉时利4225 PMU(脉冲测量单元)被用于应用编程信号和传感/读。芯片OxRAM设备的电线和NMOS晶体管实现苗条bitcell (s)。NMOS晶体管从CD4007UB CMOS双互补的一对+逆变器集成电路。在实验中,VG从外部电源供应和漏极电压(VD)/源电压(V年代使用吉时利4210大功率SMU)应用。虽然描述NMOS晶体管,被动1 kΩ放在系列的电阻器。

数据可用性

支持的数据块在本文和其他研究发现可从相应的作者在合理的请求。

引用

沃尔夫,w . a &麦基,s . a .内存墙:明显的影响。ACM SIGARCH计算机体系结构的消息23,20 - 24 (1995)。

霍洛维茨,m . 1.1计算的能源问题(我们无能为力)。在固体- - - - - -状态电路会议消化技术论文(globalfoundries),2014年IEEE国际10 - 14 (IEEE 2014)。

Milojicic D。等。计算内存,重新审视。在分布式计算系统2018年IEEE 38国际会议(ICDCS),1300 - 1309,https://doi.org/10.1109/ICDCS.2018.00130(2018)。

轩尼诗,j·l·&帕特森,d . A。计算机体系结构:量化方法(爱思唯尔,2011)。

陈,中州。,Krishna, T., Emer, J. S. & Sze, V. Eyeriss: An energy-efficient reconfigurable accelerator for deep convolutional neural networks.IEEE固态电路杂志》上52,127 - 138 (2017)。

Pawlowski, j . t .混合内存立方体(hmc)。在2011年IEEE热芯片23研讨会(高碳钢)上皮(IEEE 2011)。

李,d . U。等。1.2 v 25.2 8 gb举办128 gb / s高带宽内存(hbm)堆放dram有效microbump i / o测试方法使用29海里过程和tsv。在固体- - - - - -状态电路会议消化技术论文(globalfoundries),2014年IEEE国际,432 - 433 (IEEE 2014)。

Sze V。,陈,中州。,Yang, T.-J. & Emer, J. S. Efficient processing of deep neural networks: A tutorial and survey.IEEE学报》105年,2295 - 2329 (2017)。

Wong H.-S。p &萨拉赫丁美国记忆导致更好的计算方法。自然纳米技术10191 (2015)。

林,E。,Rosezin, R., Tappertzhofen, S., Böttger, U. & Waser, R. Beyond von neumann—logic operations in passive crossbar arrays alongside memory operations.纳米技术23305205 (2012)。

你,T。等。利用记忆性bifeo3双层结构紧凑的顺序逻辑。先进功能材料24,3357 - 3365 (2014)。

高,S。等。完整的布尔逻辑函数的实现在单一互补电阻开关。科学报告515467 (2015)。

周,Y。等。16个布尔逻辑与两三个步骤anti-serially记忆电阻器连接。应用物理快报106年233502 (2015)。

Kvatinsky, S。等。Magic-memristor-aided逻辑。IEEE电路和系统II:表达内裤61年,895 - 899 (2014)。

王,Z.-R。等。功能完整的布尔逻辑1 t1r电阻随机存取存储器。IEEE电子器件信38,179 - 182 (2017)。

黄,P。等。可重构的非易失性逻辑业务大规模电路电阻切换横梁数组。先进材料28,9758 - 9764 (2016)。

太阳,Z。,Ambrosi, E., Bricalli, A. & Ielmini, D. Logic computing with stateful neural networks of resistive switches.先进材料30.,1802554 (2018)。

金,k . M。等。单细胞状态逻辑使用dual-bit记忆电阻。自然史地位苏(RRL)快速研究快报13,1800629 (2019)。

瑟哈德里,V。等。范围:使用商品dram内存加速器为散装逐位操作技术。在第50届IEEE学报》上/ACM国际研讨会微体系结构273 - 287 (ACM, 2017)。

Agrawal)。,Jaiswal, A., Lee, C. & Roy, K. X-sram: Enabling in-memory boolean computations in cmos static random access memories.IEEE电路和系统I:普通文件1 - 14 (2018)。

太阳,X。,Liu, R., Peng, X. & Yu, S. Computing-in-memory with sram and rram for binary neural networks. In2018年第14届IEEE国际会议上固体- - - - - -州和集成电路技术(ICSICT)1 - 4 (IEEE 2018)。

周,y。等。非易失性可重构时序逻辑在高频振荡器2电阻随机存取存储器阵列。纳米级9,6649 - 6657 (2017)。

Indiveri, g . & Liu研究所。在神经形态记忆和信息处理系统。IEEE学报》103年,1379 - 1397 (2015)。

王,J。,Park, D., Papakonstantinou, Y. & Swanson, S. Ssd in-storage computing for search engines.IEEE计算机(2016)。

常,c c。等。减轻重量不对称非线性更新影响硬件基于模拟电阻突触的神经网络。IEEE杂志在新兴和选定的主题在电路和系统8,116 - 124 (2018)。

陈,W.-H。等。65 nm 1 mb的非易失性computing-in-memory reram宏观与sub-16ns大量增殖和积累为二进制ai边缘款处理器。在2018年IEEE国际固体- - - - - -状态电路会议- - - - - -(globalfoundries),494 - 496 (IEEE 2018)。

在香港,X。等。氧化物rram材料神经形态计算。材料科学杂志1-27 (2018)。

Benoist,。等。28 nm先进cmos ram电阻作为嵌入式非易失性内存解决方案。在可靠性物理研讨会,2014年IEEE国际2 e-6 (IEEE 2014)。

Vasilakis,大肠arm处理器的指令级能量特征。海勒斯研究和技术的基础,本月。计算机科学的,科技。代表。出来- - - - - -ICS/TR- - - - - -450年(2015)。

Maqsood, T。等。利用深内存层次结构来减少能源消耗和数据访问延迟单片机云计算机上。IEEE可持续的计算2,154 - 166 (2017)。

IEEE。更多的摩尔白皮书,IEEE太少了,https://irds.ieee.org/images/files/pdf/2016_MM.pdf(2016)。

卫星,B。,Goetschalckx, K., Berckelaer, N. V. & Verhelst, M. Minimum energy quantized neural networks. In2017年第51艾斯洛玛尔会议信号,系统,和电脑(IEEE 2017)。

梁,S。阴,S。刘,L。,Luk, W. & Wei, S. FP-BNN: Binarized neural network on FPGA.Neurocomputing275年,1072 - 1086 (2018)。

吴,S.-L。等。基于0.5 - v 28 256 - kb mini-array 6 t SRAM vtrip-tracking write-assist。IEEE电路和系统I:普通文件64年,1791 - 1802 (2017)。

许,C.-W。等。3 d垂直TaOx /二氧化钛RRAM超过103自整流比和子任务μ一个操作电流。在2013年IEEE国际电子设备的会议(IEEE 2013)。

Degraeve, R。等。的原因和后果的纤维rram随机方面。微电子工程147年,171 - 175 (2015)。

Sassine G。等。Sub-pJ消费和延迟时间短在RRAM阵列高耐力的应用程序。在2018年IEEE国际可靠性物理研讨会(irp)(IEEE 2018)。

许,C.-W。等。自整流双相道x/TiO2RRAM以精良的耐力超过1012对三维高密度存储类记忆周期。在2013年研讨会上超大规模集成技术T166-T167 (IEEE 2013)。

确认

作者感谢教授wen wei吴的小组从材料科学与工程部门的变与TEM表征提供帮助。T.H.侯要感谢科技部的支持(台湾)和教育部(台湾)。M。年代uri would like to acknowledge the support of DST SERB CORE Research grant (CRG/2018/001901).

作者信息

作者和联系

贡献

硕士和S.K.K.概念化原来苗条的方法和启动工作。T.H.H.,C.C.C. and B.H. fabricated the OxRAM devices. SLIM bitcell characterization, experimental demonstration and application performance analysis was performed by S.K.K., V.P. and M.S. All authors contributed to discussions, reviews and manuscript revisions.

相应的作者

道德声明

相互竞争的利益

作者宣称没有利益冲突。

额外的信息

出版商的注意施普林格自然保持中立在发表关于司法主权地图和所属机构。

补充信息

权利和权限

开放获取本文是基于知识共享署名4.0国际许可,允许使用、共享、适应、分布和繁殖在任何媒介或格式,只要你给予适当的信贷原始作者(年代)和来源,提供一个链接到Creative Commons许可,并指出如果变化。本文中的图片或其他第三方材料都包含在本文的创作共用许可,除非另有说明在一个信用额度的材料。如果材料不包括在本文的创作共用许可证和用途是不允许按法定规定或超过允许的使用,您将需要获得直接从版权所有者的许可。查看本许可证的副本,访问http://creativecommons.org/licenses/by/4.0/。

关于这篇文章

引用这篇文章

Kingra,”栏目Parmar, V。常,CC。et al。苗条:同时Logic-in-Memory计算利用双层模拟OxRAM设备。Sci代表102567 (2020)。https://doi.org/10.1038/s41598 - 020 - 59121 - 0

收到了:

接受:

发表:

DOI:https://doi.org/10.1038/s41598 - 020 - 59121 - 0

本文引用的

小说对于非传统的计算硬件和概念

科学报告(2020)